# A Mostly-Clean DRAM Cache for Effective Hit Speculation and Self-Balancing Dispatch

Purdue

Research

**Motivation:**

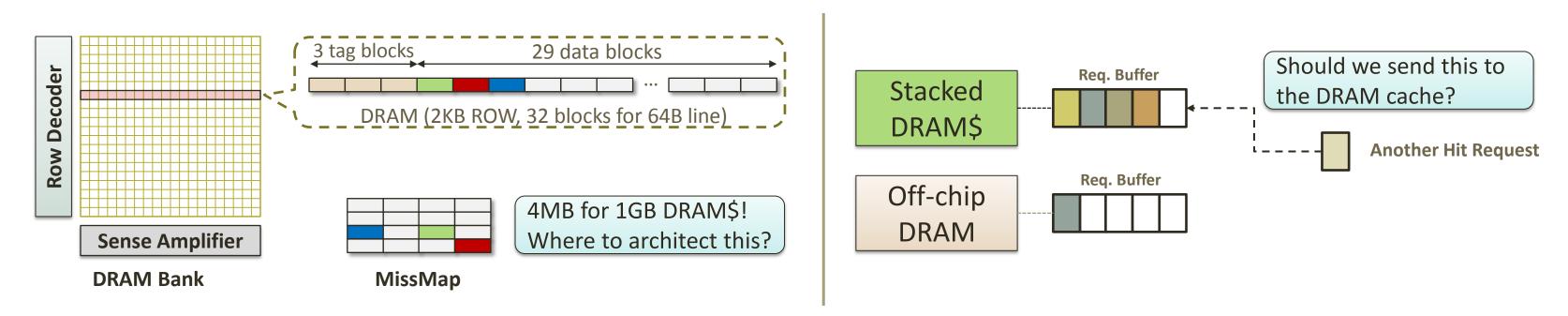

- The cache line tracking structure (MissMap) to avoid a DRAM cache access on a miss is too expensive and less practical

- Applying a conventional cache organization to DRAM caches makes the aggregate system bandwidth under-utilized

- Dirty data in DRAM caches severely restrict the effectiveness of speculative techniques

Mithuna Thottethodi

Gabriel H. Loh Mike O'Connor

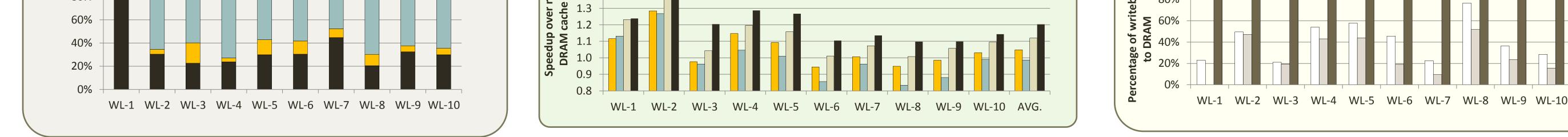

### **Our Solution: HMP + SBD + DiRT**

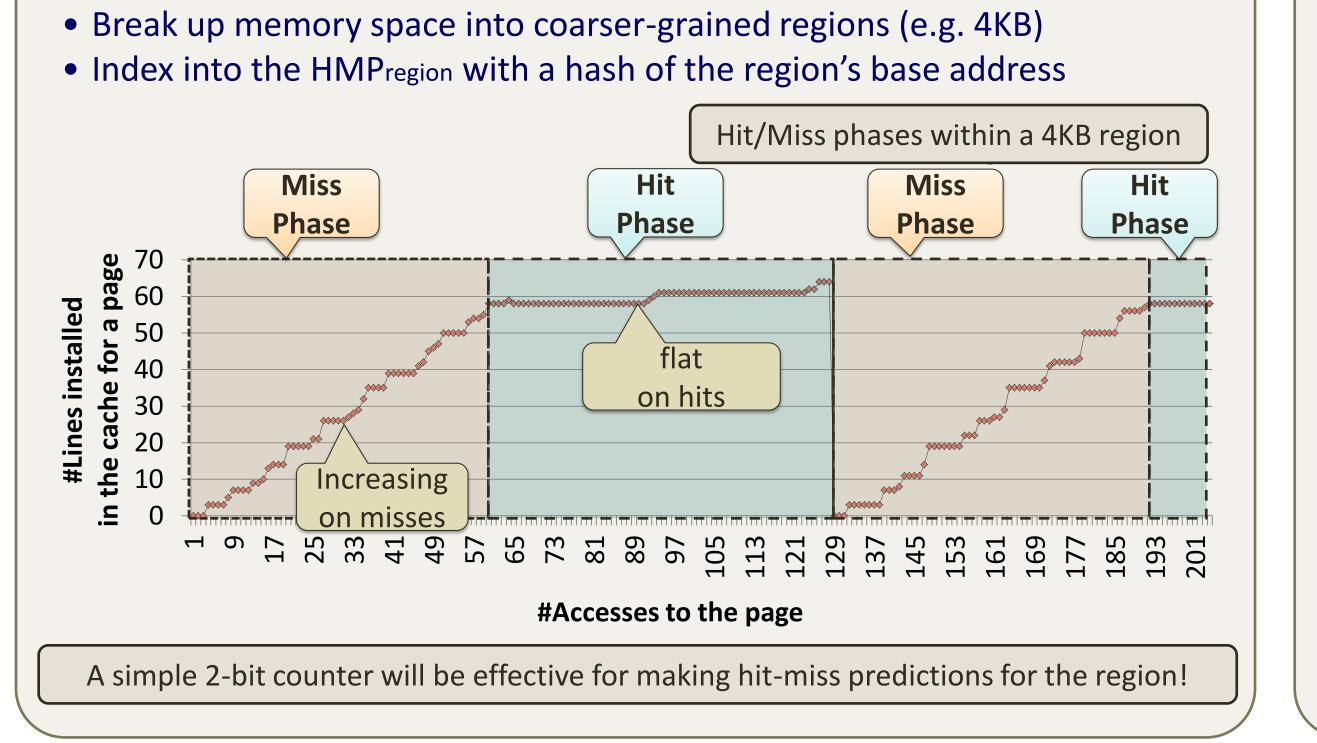

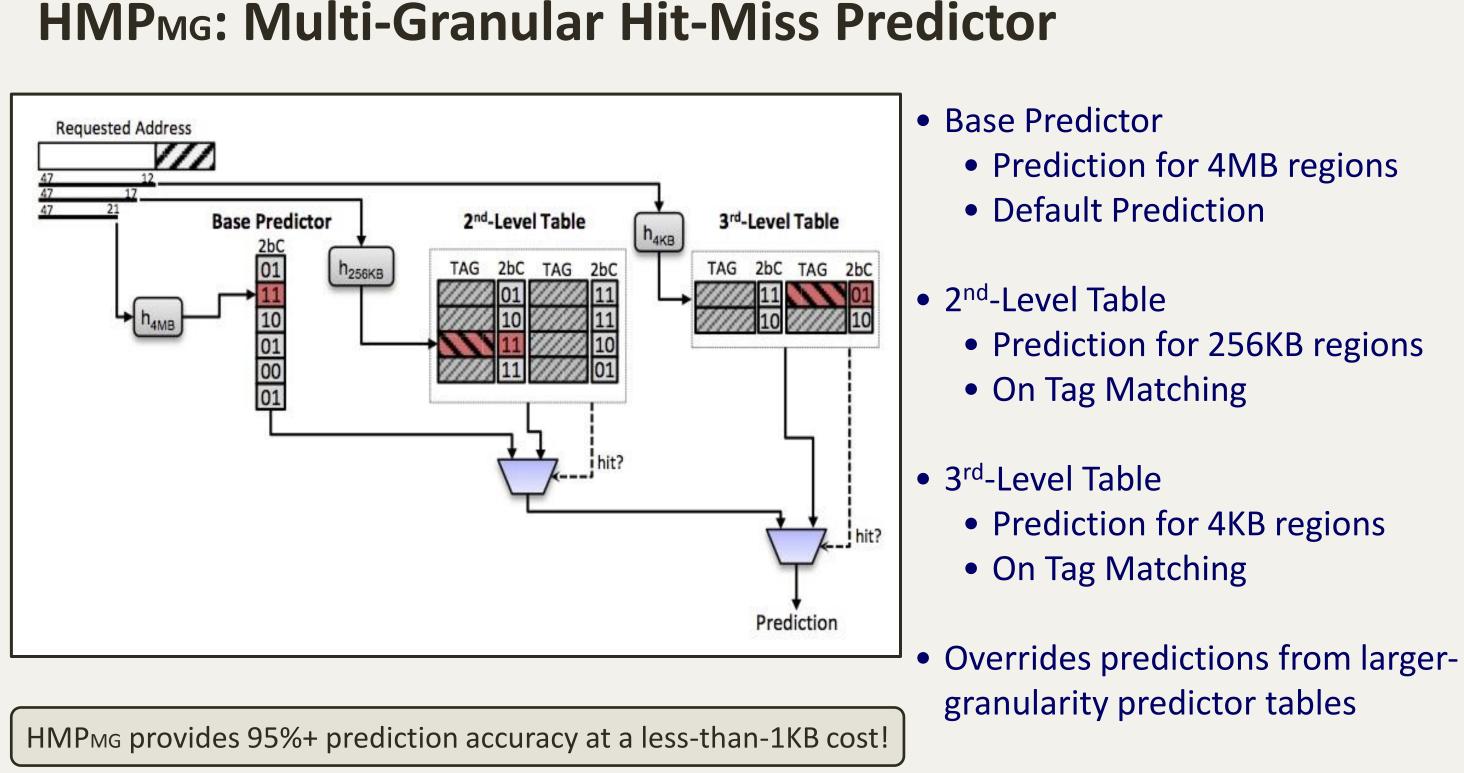

**HMP**region: **Region-Based Prediction**

Input (Clean or Dirty) to HMP and SBD

• Use a low-cost hit-miss predictor to avoid a DRAM cache access on a miss (HMP)

Comparch Jaewoong Sim Hyesoon Kim

- Steer hit requests to either a DRAM cache or off-chip memory based on the expected latency of both memory sources (SBD)

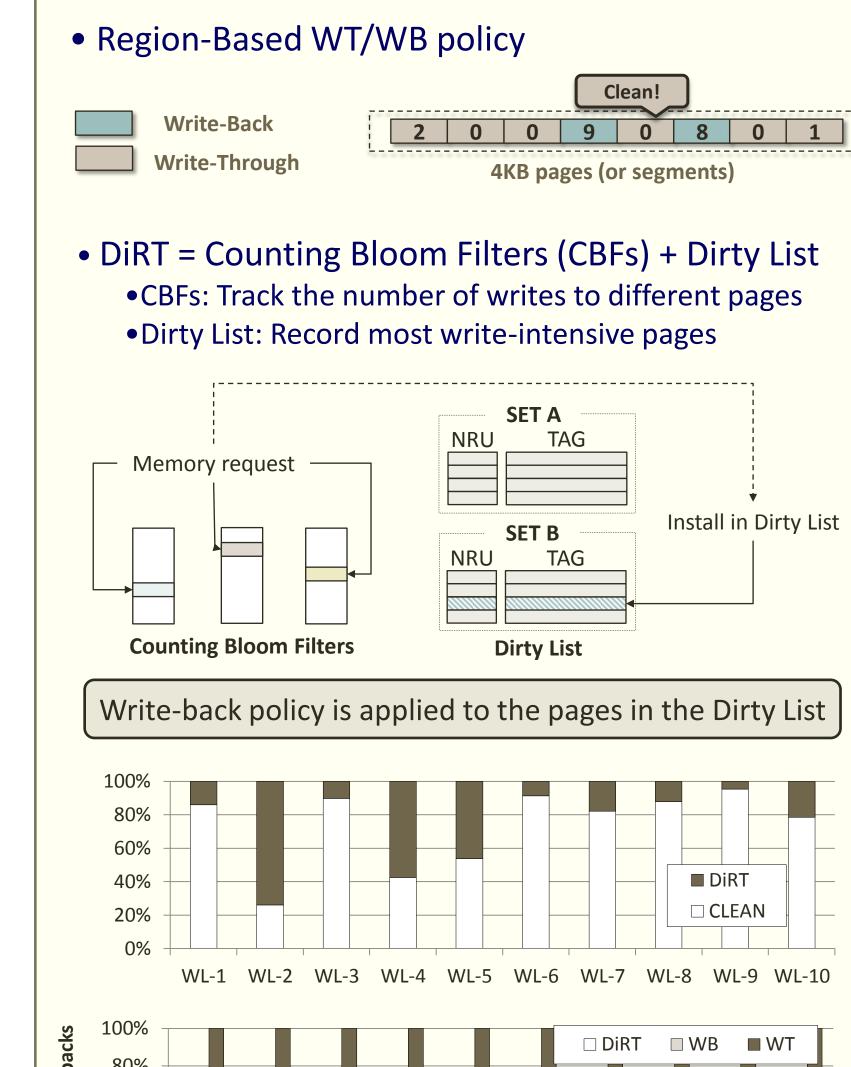

- Maintain a mostly-clean DRAM cache via region-based WT/WB to guarantee the cleanliness of a memory request (DiRT)

## Self-Balancing Dispatch (SBD)

Steer hit requests to a DRAM cache or off-chip memory based on the expected latency of both memory sources

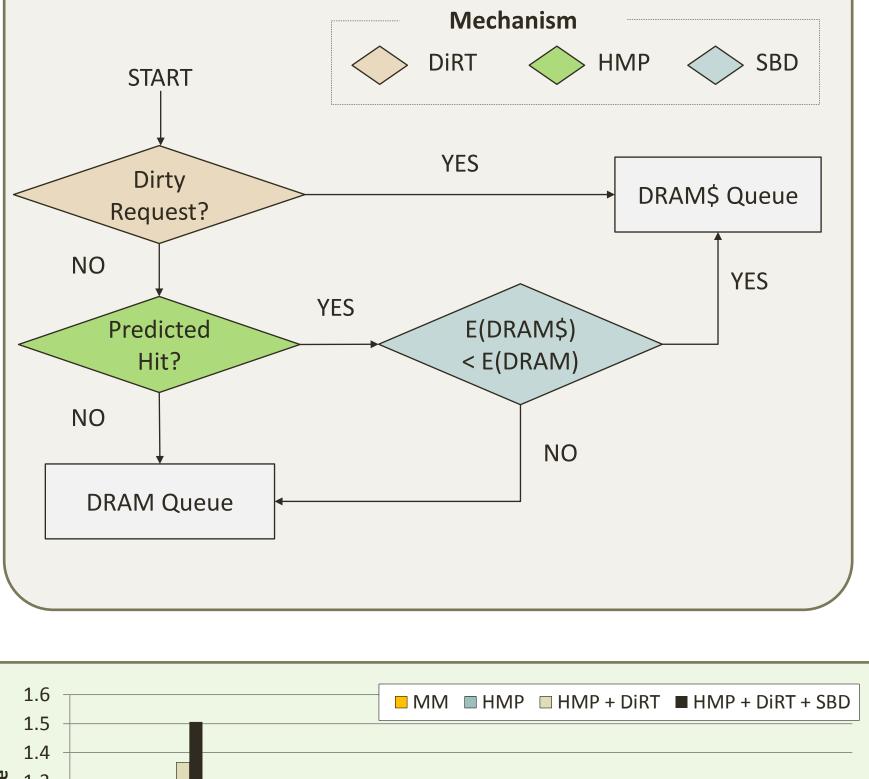

#### Algorithm: Self-Balancing Dispatch

- $N_{Off-Chip}$ : # of requests already waiting for the same bank in the off-chip memory

- $L_{off-Chip}$ : Typical latency of one off-chip memory request, excluding queuing delays  $E_{off-Chip}$ :  $N_{off-Chip} \times L_{off-Chip}$  (total expected

- queuing delay for off-chip)

- $N_{DRAM\_Cache}$ : # of requests already waiting for the same bank in the DRAM cache

- $L_{DRAM\_Cache}$ : Typical latency of one DRAM cache request, excluding queuing delays  $E_{DRAM\_Cache}$ :  $N_{DRAM\_Cache} \times L_{DRAM\_Cache}$  (total expected queuing delay for DRAM cache)

- →  $E_{Off-Chip} < E_{DRAM\_Cache}$ : send request to off-chip →  $E_{Off-Chip} \ge E_{DRAM\_Cache}$ : send request to DRAM\$

100%

80%

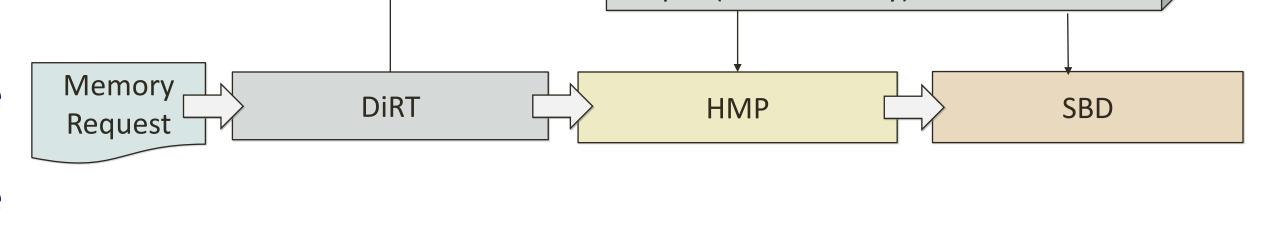

## **Putting It All Together**

- HMP, SBD, and the DiRT can be accessed in parallel

- Based on the outcomes of the mechanisms, memory requests are sent to either DRAM\$ or off-chip DRAM

## **Dirty Region Tracker (DiRT)**

0

#### The 45<sup>th</sup> Annual IEEE/ACM International Symposium on Microarchitecture (MICRO-45)